### CPE/EE 422/522 Advanced Logic Design L12

Electrical and Computer Engineering University of Alabama in Huntsville

### **Outline**

- · What we know

- How to model Combinational Networks in VHDL

- Structural, Dataflow, Behavioral

- How to model Flip flops in VHDL

- Processes

- Delays (delta, transport, inertial)

- How to model FSM in VHDL

- Wait statements

- Variables, Signals, Arrays

- · What we do not know

- VHDL Operators

- Procedures, Functions

- Packages, Libraries

- Additional Topics (if time)

07/07/2003

UAH-CPE/EE 422/522 @AM

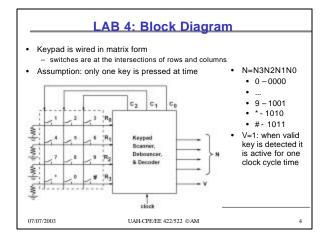

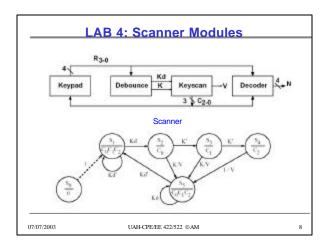

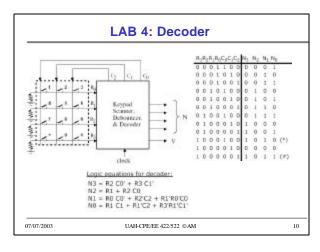

### LAB 4: Keypad Scanner

- · Lab4 preparation material

- · Telephone keypad scanner

- Section 3.5 in the textbook

- Implemented using PLD (not relevant for you)

07/07/2003 UAH-CPE/EE 422/522 ©AM 3

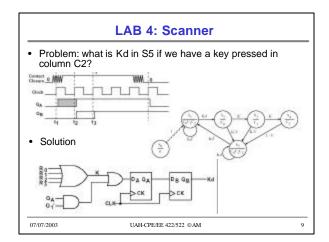

### LAB 4: Scan Procedure

- 1. Apply logic 1s to columns C0, C1, C2 and wait

- 2. If any key is pressed a 1 will appear on R0, R1, R2, or R3

- Apply 1 to column C0 only; if any of Ri's is 1, a valid key is detected; set V=1 and corresponding N

- If no key is detected in column C0 apply 1 on C1; Repeat the same for C2

- 5. When a valid key is detected, apply 1s to C0, C1, C2 and wait until no key is pressed

- ensure that only one valid signal is generated each time a key is pressed

07/07/2003

UAH-CPE/EE 422/522 @AM

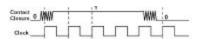

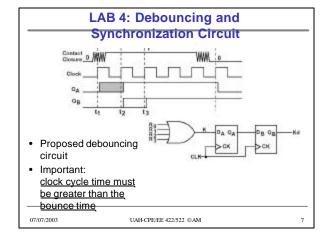

### LAB 4: Debouncing

- Problem: with mechanical switch the contact will bounce causing noise in the switch output

- contact may bounce for several milliseconds

Solution: after a switch closure has been detected, wait for bounce to settle down before reading the key

07/07/2003 UAH-

UAH-CPE/EE 422/522 @AM

### Functions execute a sequential algorithm and return a single value to calling program function rotate right (reg: bit\_vector) return bit, vector is begin return reg rer 1; end rotate right; A = "10010101" B <- rotate\_right(A);</li> General form function function-name (formal-parameter-list) return return-type is [declarations] begin securitial statements -- must include return return-value;

UAH-CPE/EE 422/522 © AM

11

07/07/2003

**Review: VHDL Functions**

### **Review: VHDL Procedures**

- · Facilitate decomposition of VHDL code into modules

- Procedures can return any number of values using output parameters

- · General form

```

procedure procedure_name (formal-parameter-list) is

[declarations]

begin

Sequential-statements

end procedure_name;

procedure_name (actual-parameter-list);

```

### **Review: Parameters for Subprogram Calls**

|                              | Class                                                 | Actual Parameter                           |                                    |

|------------------------------|-------------------------------------------------------|--------------------------------------------|------------------------------------|

| Mode                         |                                                       | Procedure Call                             | Function Call                      |

| in <sup>1</sup><br>out/inout | constant <sup>2</sup><br>signal<br>variable<br>signal | expression<br>signal<br>variable<br>signal | expression<br>signal<br>n/a<br>n/a |

|                              | variable <sup>3</sup>                                 | variable                                   | n/a                                |

| efault mode for fu           |                                                       |                                            | n/a<br>ult for out/inout med       |

### **Packages and Libraries**

- Provide a convenient way of referencing frequently used functions and components

- · Package declaration

package package-name is

package declarations

end [package][package-name];

· Package body [optional]

package body package-name is package body declarations end [package body][package name];

07/07/2003 UAH-CPE/EE 422/522 ©AM 15

# package id. (ac) is function and i (reg.) yet) bit (vectors) downto (i) (arry: bit) where it but colors return colores; function register (in the property of the property of

# Library BITLIB — bit\_pack package particle body ML 505 M The foreign of the 1 Acti is where in them a 5-bit saw feeded of the 1 Acti is where in the 1 Acti is where it is w

```

Components in Library BITLIB includes

-> Import MAD gate

easitify Aurit is

general (DELAY) terral);

part (AL, AL), is bit; Z; but bit);

easitify Aurit is

enthistoure consum of And I is

begin

Z = AL and AZ end AZ end AS affect DELAY)

end;

-D TIP-flas

enthis DIT is

general (DELAY) in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (Dir out bit);

perf (O), CLN in DIL

- is able (D), CLN in DIL

- is able

```

### **Additional Topics in VHDL**

- Attributes

- · Transport and Inertial Delays

- Operator Overloading

- Multivalued Logic and Signal Resolution

- IEEE 1164 Standard Logic

- Generics

- · Generate Statements

- Synthesis of VHDL Code

- · Synthesis Examples

- · Files and Text IO

07/07/2003 UAH-CPE/EE 422/522 ©AM 19

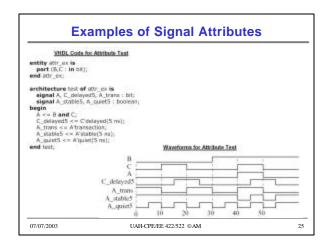

### Signal Attributes Attributes associated with signals that return a value Returns True if an event occurred during the current deta, else false STVENT True if a transaction occurred during the current delta, else false S'ACTIVE STAST EVENT Time elapsed since the previous event on S. STAST VALUE Value of S before the previous event on S STAST\_ACTIVE Time elapsed since previous transaction on S A'event - true if a change in S has just occurred A'active - true if A has just been reevaluated, even if A does not change 07/07/2003 UAH-CPE/EE 422/522 ©AM 20

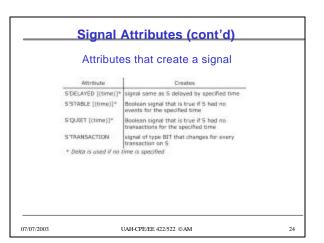

### Signal Attributes (cont'd)

- Event

- occurs on a signal every time it is changed

- Transaction

- occurs on a signal every time it is evaluated

- Example:

```

A <= B - - B changes at time T

```

|        | A'event | B'event |

|--------|---------|---------|

| т      |         |         |

| T + 1d |         |         |

07/07/2003 UAH-CPE/EE 422/522 ©AM 21

```

Signal Attributes (cont'd)

entity test is

if (A'event) then Aev := '1';

else Aev := '0';

architecture bmtest of test is

end if;

if (A'active) then Aac := '1';

else Aac := '0';

signal A : bit;

signal B : bit;

end if;

if (B'event) then Bev := '1';

else Bev := '0';

signal C : bit;

A <= not A after 20 ns;

end if;

B <= '1';

else Bac := '0';

end if;

C \le A and B;

process(A, B, C)

variable Aev : bit;

if (C'event) then Cev := '1';

else Cev := '0';

variable Aac : bit;

end if;

if (C'active) then Cac := '1';

variable Bev : bit;

variable Bac : bit;

else Cac := '0';

end if;

variable Cev : bit;

variable Cac : bit;

end process;

UAH-CPE/EE 422/522 © AM

07/07/2003

22

```

### Signal Attributes (cont'd) /test/a /test/line\_\_15/bev delta /test/b /test/line\_\_15/bac /test/c /test/line\_\_15/cev /test/line\_\_15/aev /test/line\_\_15/cac /test/line\_\_15/aac 0 +0 0 0 0 0 0 0 0 0 0 0 +1 0 1 0 0 0 1 1 0 1 0 0 0 0 1 1 0 1 1 20 +0 20 +1 1 1 1 0 0 0 1 1 1 1 0 0 1 1 40 +0 0 0 0 0 40 +1 0 0 1 1 0 1 0 0 0 07/07/2003 UAH-CPE/EE 422/522 ©AM 23

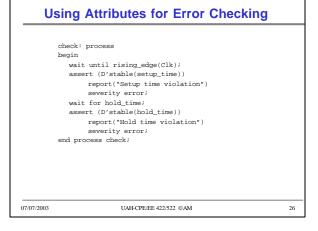

# assert boolean-expression report string-expression severity severity-level • If boolean expression is false display the string expression on the monitor • Severity levels: Note, Warning, Error, Failure

```

Recap: Adding Vectors

- This procedure adds two n-bit bit, vectors and a carry and

- returns an n-bit sum and a carry. Add1 and Add2 are expurined

- to be of the same laright and dimensioned s-1 downto 0.

procedure Addrect

(Add1,Add2: in bit, vector;

signal Sum: out bit, vector;

signal Sum: out bit, vector;

signal Cost; out bit;

n:in positive) is

variable C: bit;

begin

C:= (Add1(i) and Add2(i) ser Add2(i) ser C;

C:= (Add1(i) and Add2(ii) or (Add1(i) and C) or (Add2(i) and C);

mnd ison;

Lout <= C;

end Add0ct;

Note: Add1 and Add2 vectors must be dimensioned as N-1 downto 0.

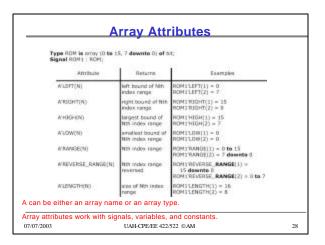

Use attributes to write more general procedure that places

no restrictions on the range of vectors other than the lengths must be same.

```

# Procedure for Adding Bit Vectors -- This procedure adds two bit, vectors and a carry, and returns a aum and a carry. Both bit, vectors should be of the same length. procedure Addive(2) (Add31,Add21 in bit, vector): CD: In bit; signal Sum: out bit, vector): (Bit in bit; signal Sum: out bit, vector): alias ni: bit; vector|Add21ength-1 dewento 0] is Add1; alias ni: bit; vector|Add21ength-1 dewento 0] is Add2; alias ni: bit; vector|Add21ength-1 dewento 0] is Sum; begin assert ((n13ength = n21ength) and (n1 length = Stength)) report "vector lengths must be equal!" sevently arror; for in siferonise; range loop S[i] <= n1(0) are n2(0) are n2(0) are C; C = (n1(0) and n2(0)) or (n1(0) and C) or (n2[i] and C]; and Addvec2; 07/07/2003 UAH-CPE/EE 422/522 @AM 30

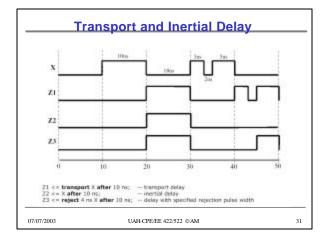

### Transport and Inertial Delay (cont'd) Z3 <= reject 4 ns X after 10 ns; Reject is equivalent to a combination of inertial and transport delay: Zm <= X after 4 ns; Z3 <= transport Zm after 6 ns; Statements executed at time T - B at T+1, C at T+2 A <= transport B after 1 ns; A <= transport C after 2 ns; Statements executed at time T Statements executed at time T -C at T + 1: -C at T + 2 A <= B after 1 ns; A <= transport B after 2 ns; A <= C after 2 ns; A <= transport C after 1 ns; 07/07/2003 UAH-CPE/EE 422/522 ©AM 32

### **Operator Overloading**

- Operators +, operate on integers

- Write procedures for bit vector addition/subtraction

addvec, subvec

- Operator overloading allows using + operator to implicitly call an appropriate addition function

- · How does it work?

- When compiler encounters a function declaration in which the function name is an operator enclosed in double quotes, the compiler treats the function as an operator overloading ("+")

- when a "+" operator is encountered, the compiler automatically checks the types of operands and calls appropriate functions

07/07/2003

UAH-CPE/EE 422/522 © AM

. . .

### VHDL Package with Overloaded Operators

### **Overloaded Operators**

- A, B, C bit vectors

- A <= B + C + 3?

- $A \le 3 + B + C$ ?

- Overloading can also be applied to procedures and functions

- procedures have the same name –

type of the actual parameters in the procedure call

determines which version of the procedure is called

07/07/2003

UAH-CPE/EE 422/522 @AM

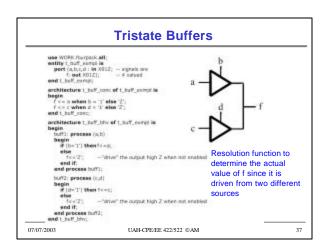

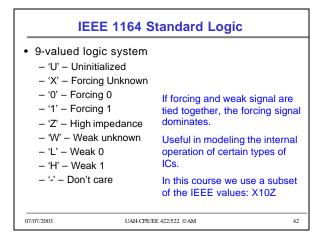

Multivalued Logic

- Bit (0, 1)

- Tristate buffers and buses => high impedance state 'Z'

- Unknown state 'X'

- e. g., a gate is driven by 'Z', output is unknown

- a signal is simultaneously driven by '0' and '1'

07/07/2003

35

UAH-CPE/EE 422/522 © AM

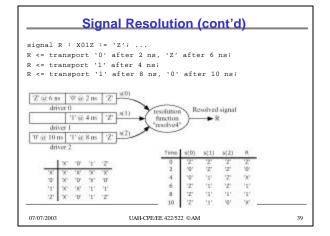

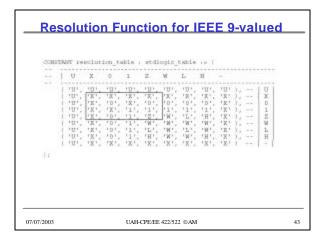

### **Signal Resolution**

- VHDL signals may either be resolved or unresolved

- Resolved signals have an associated resolution function

- · Bit type is unresolved -

- there is no resolution function

- if you drive a bit signal to two different values in two concurrent statements, the compiler will generate an error

7/07/2003 UAH-CPE/EE 422/522 ©AM 38

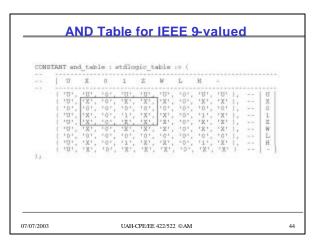

### **AND and OR Functions Using X01Z** 'X' '0' '1' 'Z' 'X' 'X' '0' 'X' 'X' '0' '0' '0' '0' '0' '1' '0' 'Z' 'X' '0' 'X' 'X' OR 'X' '0' '1' 'Z' '1' 'X' 'Χ' 'Χ' 'X' 'X' '0' 'X' '0' '1' '1' 07/07/2003 41 UAH-CPE/EE 422/522 @AM

### AND Function for std\_logic\_vectors

07/07/2003

```

function "and" [ | : std_ulogic; r : std_ulogic ] return UND1 is begin return (and_table(), r)]; std_ulogic ] return std_logic_vector | indicate | return std_logic_vector | return std_logic_vector is allies in : std_logic_vector | to the NGTH | is 1; size in : sd_logic_vector | to the NGTH | is 1; size in : sd_logic_vector | to the NGTH | is 1; size in : sd_logic_vector | to the NGTH | is 1; size in : sd_logic_vector | to the NGTH | is 1; size in : sd_logic_vector | to the NGTH | is 1; size in : sd_logic_vector | to the NGTH | is 1; severity | return | result result | return | retu

```

UAH-CPE/EE 422/522 @AM